0756-8632035

以客户为中心

新闻动态

NEWS

由摩尔精英主办的《半导体测试经济学》线上研讨会反响热烈。研讨会从测试对产品盈利的直接或间接影响、测试中显性及隐性成本的深度剖析以及如何避免量产测试中的误区等角度进行分享。在会中及会后我们收到了许多与会嘉宾提出的问题。在此我们将通过本期内容,汇总此次研讨会中收集的热点话题进行进一步的解答。

误区1:

为了达到量产测试高的UPH (Unit Per Hour) 必须使用贵的高端测试机?

分析:

● 通常,贵的高端测试机的仪器资源数目比较多而且性能也比较高。

● 仪器资源数的增加能增加同测数从而提高量产测试的UPH。

● 测试机配有昂贵的高性能仪器主要目的是提升特征性测试(characterization test)的覆盖率,并不是为了提高量产UPH。相反,在大部分情况下,仪器的高性能在量产测试中并不一定被使用,反而会增加测试机的折旧成本而增加量产测试费用。

◆ 观众提问一:

在量产的时候如果能用高端测试机测试,比如Serdes、PCIE等高速接口用高端设备测,是否有更好的覆盖率及更好的质量?如果用便宜的设备测试性价比该怎么评估?

◇ 摩尔精英建议:

首先,在任何大规模生产中,生产成本一定是我们最优先考虑的事。因此,采用“最合适而不是最昂贵、最高端的ATE测试设备”来开发量产测试方案是芯片测试工程决策人首先要考虑的原则。其实,芯片测试的覆盖率、测试的质量,和所用的机台的性能并不是100%正相关。量产和验证不同,芯片量产测试方案的开发,应该以defect-oriented为指导思想,提升覆盖率,保障质量。在Defect-oriented的原则下,并不是所有测试项目都需要最高规格的仪器。再次,对于Serdes,例如PCIE,目前应用已经在10Gbps以上,例如PCIE Gen4.0数据速度为16GT/s, PCIE Gen5.0 数据速度为32GT/s。这些都已经超过目前业内最新、最昂贵的ATE机台的高速数字板卡所能覆盖的范围。对于high-speed IO, 最好的量产测试方法还是做tx/rx loopback test。

总而言之,应该选择适合所测芯片的ATE测试机,而不是“只买贵的、不买对的”。

◆ 观众提问二:

为什么说高性能测试项在量产测试中并不是必须的?难道保证品质不是最重要的吗?

◇ 摩尔精英建议:

对于一些特高性能的测试项,比如高速数据接口,在量产中如果直接进行测试,一方面对测试机要求比较高,另一方面量产测试稳定性也比较难以控制。对于一个经过Characterization验证过设计合格的产品,我们在量产中可以采用defect-oriented测试方案,如在DFT(Design for Test)中设计一些BIST或Loopback方案,也可以在测试板上采用golden units对测的方案。如果设计很Marginal必须要直接测量这些参数,我们就必须使用昂贵高端测试机或外挂实验室设备进行量产,量产测试流程在工厂端也需要进行比较好的监控和维护。

误区2:

FT是量产测试的最后测试环节,为了保证质量,FT必须要有高的测试覆盖率吗?

分析:

● 对于一个设计合格的芯片,坏品主要是从晶圆制造和封装这两个生产流程引入的。CP测试可以分离出晶圆制造引入的坏品;FT测试除了可以分离出晶圆制造引入的坏品,还能分离出封装引入的坏品。

● CP流程的设立主要是为了:提高FT的良率以免除坏品的封装费用;提供封装后无法完成的测试。

● 通常,海量芯片的测试包含CP和FT,CP+FT覆盖整个芯片的所需的测试。根据芯片的特点,可以合理分配测试项在CP和FT流程中。

【实例】 一个简单的模拟电源管理芯片,原先只有FT测试,但由于受限于分选机,只能并测4工位,无法满足封测厂的UPH要求。因此,新增了CP流程,并测数为16。经合理分配测试项,FT注重由封装引入的故障对应的测试项,其它都由CP覆盖。最终,FT不但满足封测厂的UPH要求,而且整体测试方案不但保证的产品质量也降低了测试费用。

◆ 观众提问三:

FT不增加覆盖率,都放CP测,那封装引入的故障被漏掉改怎么办?怎么区分哪些测试项应该放CP,哪些应该放FT,哪些两边都要放?

◇ 摩尔精英建议:

CP不能覆盖封装引入的defect,而且封装也会影响芯片的一些性能参数,FT必须覆盖CP不能覆盖的测试项和受封装影响的测试项。如何分配CP和FT的测试项,需要和设计工程师协助完成。

另外,还需要考虑芯片的特点和测试硬件的费用和性能。例如,我以前的手机模拟芯片有300+ pads,如果CP要测8工位,需要用昂贵的垂直针。因为工艺比较成熟良率也比较高,我们决定CP用悬臂针测2工位,测试项主要包含有良率损失的测试项。

误区3:

量产测试必须要测产品规范书上的所有参数和使用产品规范书上的上下限吗?

分析:

● 传统定义:好的产品是完全符合技术规范的产品。要保证一个产品是好的,必须:

○ 测试每个规范书上的参数;

○ 进行老化测试保证使用寿命;

○ 完成用户端的校对。

● 实用定义:好的产品 = 好的设计 + 好的制造

○ 好的设计:通过设计验证和多个process lots的特性测试,产品的参数符合技术规范的要求;

○ 好的制造:没有制造引入的defects和outliers。

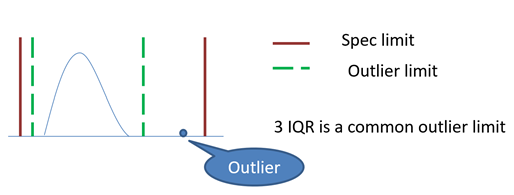

● 对于一个设计合格的产品,量产测试的重点是快速找出制造过程中导入的defects和outliers。量产测试是一个defect-oriented test。

图:defect-oriented test

◆ 观众提问四

我们怎么预判芯片会有哪些defects和outliers?然后再针对可能会有的问题,去设计最小化的测试来覆盖,成本是降低了,那么质量该如何保证?

◇ 摩尔精英建议:

Defect必须在量产测试中被screen out,而且可以有针对地被快速查出来。有些测试项尽管测试结果在spec limits里面,但根据数据分布属于outlier,其实也建议被screen out,量产测试的limits可以通过数据分析来制定。

好的芯片产品 = 好的设计 + 好的制造。好的设计除了设计工程师的设计和大量仿真,更重要的是要结果严格的design verification、qualification和characterization来验证。其实,只有设计合格的产品才能投入量产,否则会有良率等问题。对于,合格设计的产品,量产测试的目的不是设计最小化测试,而是设计最有效的测试将生产引入的defects快速地查出来,量产测试是一个defect-oriented测试。

误区4:

封装和测试必须在同一个厂吗?

分析:

● 封装和测试在同一个厂的优点:

○ 减少运输过程花费的时间;

○ 减少运输的费用和可能带来的质量风险。

● 封装和测试分开的优点:

○ 产能灵活,不受制于封装厂内测试产能;

○ 质量管理增强,区分晶圆与封装质量问题;

○ 供应链管理能力增强,多封装厂订单管控增强。

◆ 观众提问五:

在晶圆厂到封装厂中物流发生的风险到底有多大?

◇ 摩尔精英建议:

我在这个行业工作30多年了,其实在物流的风险上看到的案例也不是很多,甚至许多误操作呢(例如晶片的处置不当, IC混料,数量算错,错误寄送等等)会甩锅给物流,其实现在包装的技术相当的不错, 也有Drop test等手段在验证产品的 鲁棒性(Robustness) ,可以说大家都做了很多,物流对于品质的冲击是可以预测的,物流风险更多的其实是成本的问题,而目前这个成本是可以通过保险的方式覆盖的,万分之八左右的保费相比于成本而言是相对可控的。

最后插几句我个人的所见所想,我在行业内这么多年看到在物流中发生的"遗失",其实发现有部分都是"内贼"搞出的问题,在DRAM疯狂涨价的时代,的确有一些不好的失窃甚至是抢劫问题,后来也证明是里应外合的产物。在一些地区除了失窃,物流环节的其他实际货损倒是少见。最后建议大家在考虑物流风险上面,除了保险等手段,还可以在芯片的设计端增加更多的Tracebility(Efuse/OTP/MTP),不光可以保证芯片供应链安全,还可以增加更丰富的管理手段。

版权声明: 本站内容除原创文章之外,转载内容只为传递更多信息,并不代表本网站赞同其观点。转载的所有的文章、图片、音/视频文件等资料的版权归版权所有权人所有。本站采用的非本站原创文章及图片等内容无法一一联系确认版权者。如涉及作品内容、版权和其它问题,请及时通过电子邮件或电话通知我们,以便迅速采取适当措施,避免给双方造成不必要的经济损失。联系电话:0756-8632035;邮箱:zhcce@chnchip.com.cn。