0756-8632035

以客户为中心

新闻动态

NEWS

关于摩尔定律的消亡,近来有很多讨论。连续工艺节点的场效应晶体管密度的增加已从上一代每2 1/2年的2倍速度减慢。摩尔在50年前发表的评论的经济性质也受到了审查-每个晶体管的成本降低也有所 减少。

由于以下方面的要求,传统的技术缩放模型已变得更加复杂:替代沉积和蚀刻设备;引入新的互连和介电材料;并且,越来越依赖于新的设计技术协同优化(DTCO)集成方法。

顺便说一句,各种2.5D和3D多管芯封装产品的出现导致使用了“摩尔定律”集成一词。这些封装中管芯功能和工艺选择的潜在多样性为实现有效 密度和成本提供了其他折衷,这是摩尔定律的基础。

尽管有关于摩尔定律的所有评论,但仍存在对新设备的巨大研发投资,这些新设备将继续提供改进的性能,功率和面积。在由SEMI主办的最近的高级半导体制造会议(ASMC)上,一个重点是Intel的Design Enablement副总裁兼总经理Gary Patton的主题演讲,他概述了这些研发工作。他的“摩尔定律”演讲对未来的技术功能提出了乐观的看法。

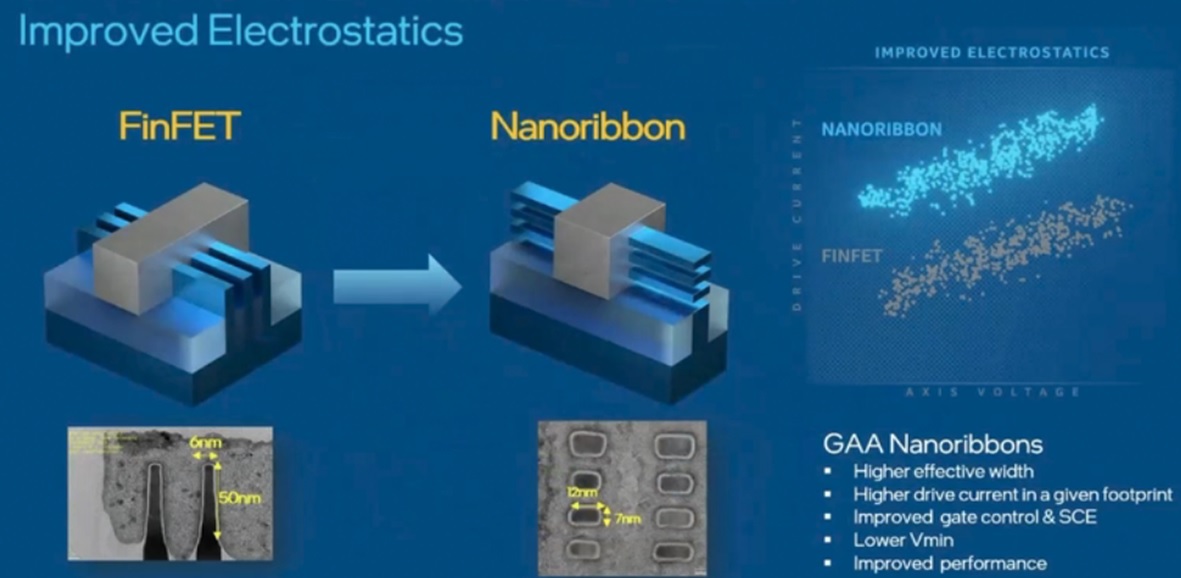

加里介绍了向全栅极(GAA)器件的过渡,该器件有望成为FinFET的直接后继产品。(随着重新引入单个晶体管宽度又是设计参数的设备,可能需要重新解释晶体管/ mm ** 2密度度量。)

作为CMOS以外的潜在的长期过渡,正在开展许多研究计划 ,例如2D半导体材料(的阵列),例如MoS2,WS2和WSe2。

在Gary的演讲中,特别值得注意的是对工艺技术开发领域的描述,该领域可能未得到应有的考虑-异质半导体材料的3D单片集成,用于制造优化的nFET和pFET器件。这种方法提供了持续的器件缩放,成熟工艺制造技术的集成,并且建立在现有(基于CMOS)电路设计经验的基础上。

在详细介绍某些整体式3D可能性之前,对异质材料的结合进行描述将是很有见地的。

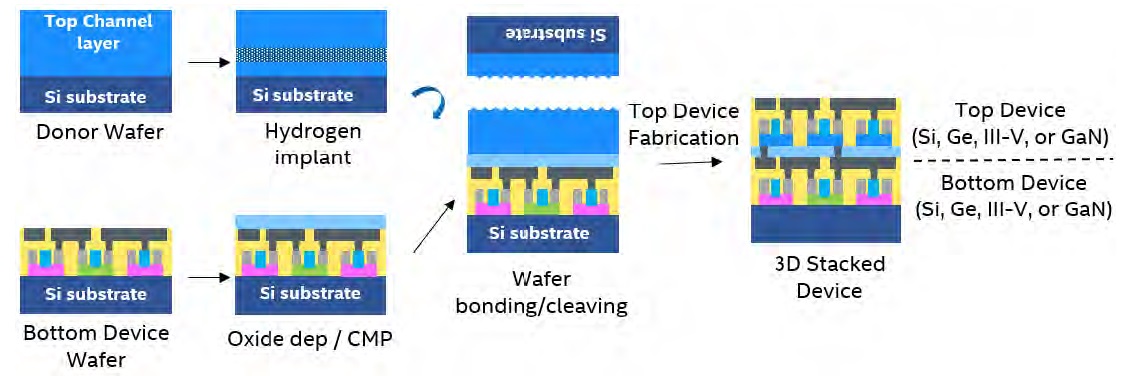

氧化物键合和施主晶圆切割

单片3D集成的目标是为设备制造提供多种堆叠的半导体材料。在主晶片中制造晶体管的子集。随后,将(不同半导体组成的)施主晶片结合到主体上,并劈开以在主体顶部上提供薄材料层,以用于后续的器件处理。下图说明了晶圆处理流程。

全厚度主晶圆提供机械支撑;薄的施主层不会显着增加整体厚度,从而可以使用现有的处理设备和制造流程。(正如不久将要讨论的那样,在处理供体层设备的热预算方面存在一些限制,以免对现有的主机设备特性产生不利影响。)

简而言之,准备3D整体堆栈的步骤顺序为:

- 器件在主体(300毫米)晶圆上制造

- 主机晶片接受薄介电层的沉积(例如,SiN和SiO2的化学气相沉积)

- 抛光主机晶片表面(例如,使用化学机械抛光)

- 使用优化的注入能量和剂量,对一个(300mm)供体晶圆进行H +(质子)注入

- 供体晶圆和主晶圆键合

在键合主体和施主晶片之前,采用特定的晶片表面清洁化学方法。两个晶片表面必须是亲水的,“原子上光滑的”并且具有高密度的化学键合位点(以防止在界面处形成微孔)。

在特殊的对准器(带有双晶片卡盘)中,主晶片和施主晶片彼此相对放置,对准并接触。在初始的晶圆对晶圆界面键合稳定之后,释放施主卡盘。

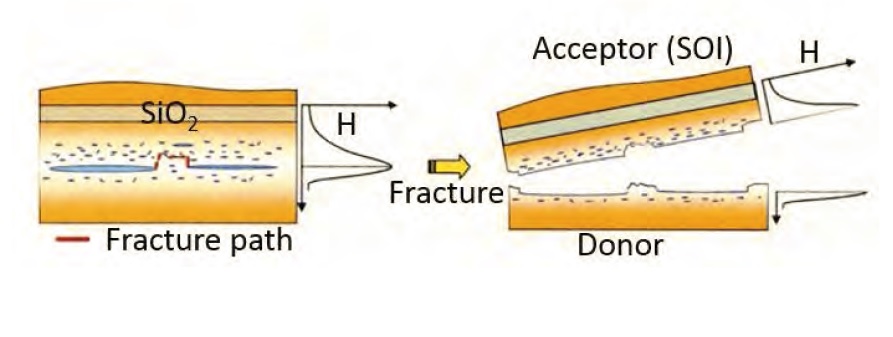

然后,对复合材料进行热退火步骤。该退火具有两个关键功能: 加强键合界面,并允许注入的氢在半导体晶体中扩散,并成核形成H2。

在施主晶片中会形成一个非常薄的H2层,其深度等于H +注入后最高的晶体位错点。该H 2层在施主晶片晶体内引入了结构上较弱的界面。

- 供体晶圆在内部H2界面处被劈开

机械边缘力和/或热循环的组合导致供体晶片在H2层深度处破裂。

- 将得到的具有堆叠的半导体层序列的单片晶圆退火(以减少残留的植入物损坏),并进行抛光

如上所述,破裂步骤可导致粗糙的表面形貌,该粗糙的表面形貌需要在随后的器件制造和层到层接触形成之前被抛光。

多年来,这种用于氧化物键合和施主层转移的技术已用于绝缘体上硅(SOI)晶片制备的生产中。(对成核退火步骤中H +扩散,H2层形成以及对施主晶片晶体的结构影响的深入了解仍然是研究的活跃领域。)

加里的演讲重点介绍了英特尔研究部门正在将这一层转移技术应用于3D单片集成的两个领域,以进一步扩展摩尔定律。

Si中的nFET,Ge中的pFET

先进工艺开发面临的问题之一是Si中相对较弱的空穴迁移率,尤其是在较高的空穴自由载流子密度和电场下。当前的工艺技术在pFET器件通道中引入了压缩机械应力,以提高空穴迁移率。最近的进步致力于直接在pFET器件通道中利用化学计量的Si和Ge的组合-即Si(x)Ge(1-x)-来利用Ge中更高的空穴迁移率。

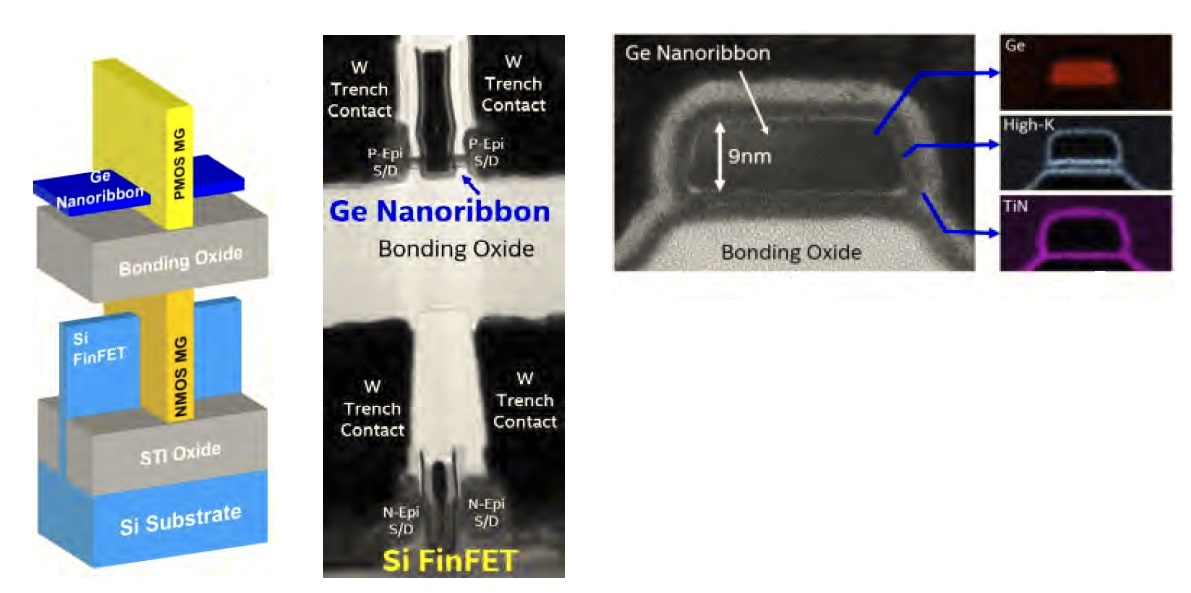

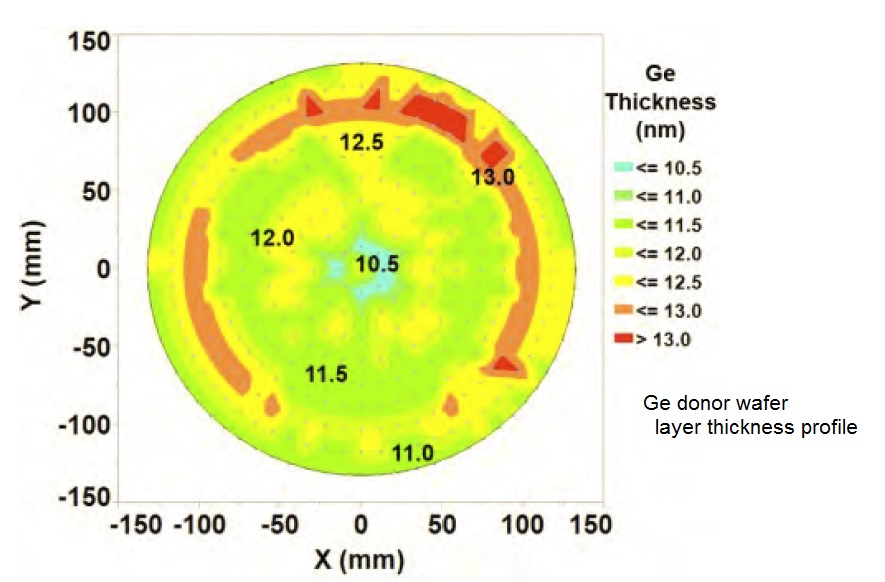

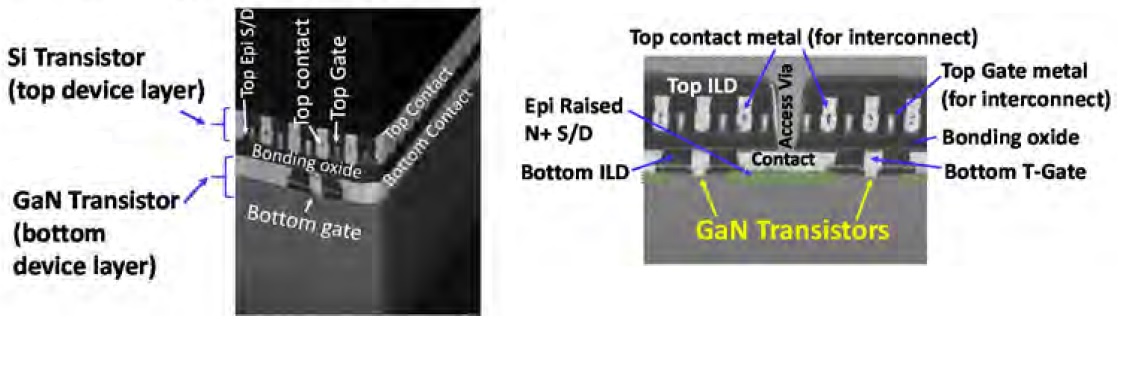

英特尔研究团队一直在使用3D单片集成技术,该技术使用键合在Si主晶片顶部的Ge施主层,如下图所示。[1]

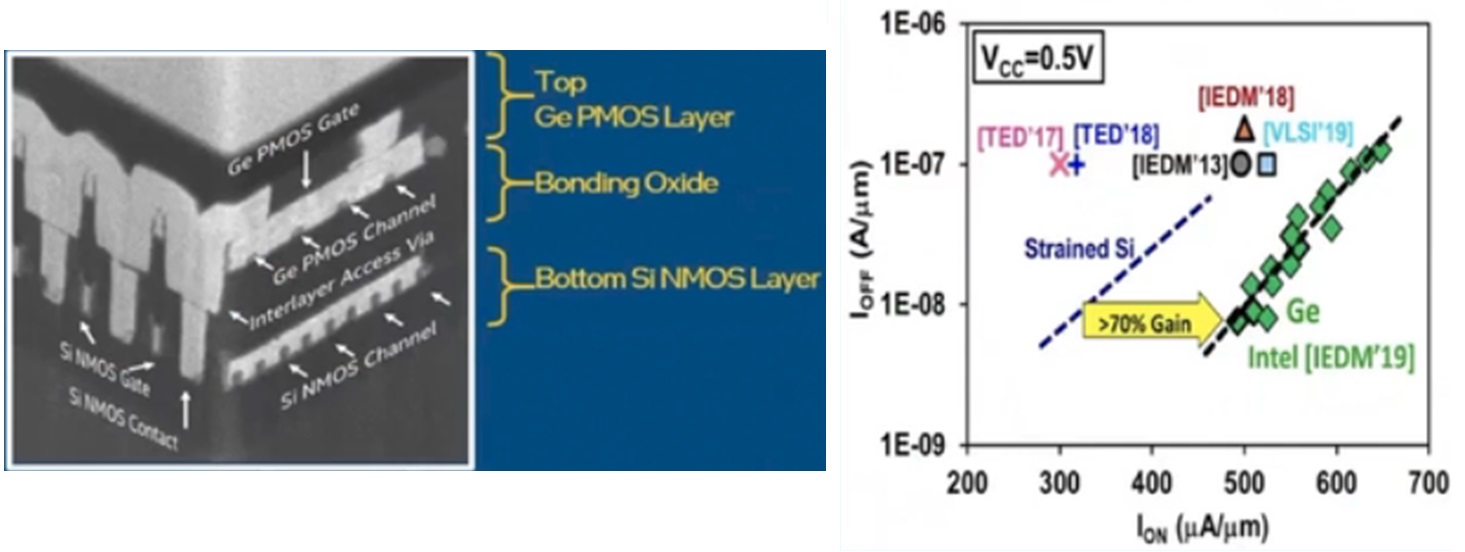

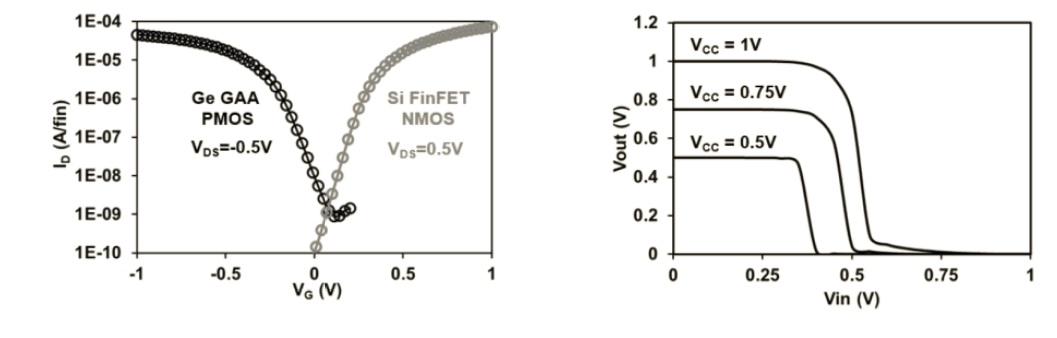

在这种情况下,在用于nFET的主晶圆上制造了FinFET器件结构,而在Ge供体层中的pFET使用了GAA拓扑。如上所述,选择nFET高K,金属栅极,源/漏掺杂外延和接触金属的工艺流程和材料选择,使其与Ge施主层的后续热处理和pFET的制造兼容(例如, <600C)。

在制造GAA pFET源极/漏极Epi,器件氧化物和金属栅极(使用替换栅极工艺)以及源极/漏极触点之后,在两个晶体管层之间形成通孔。

上面还说明了一个300mm晶圆上的Ge供体层厚度的示例分布图,显示了整体层转移工艺的出色均匀性(整个晶圆上的变化<3nm)。

下图显示了3D单片反相器逻辑门(低至VCC = 0.5V)的最终3D横截面,(短通道)Si nFET和Ge pFET特性,以及Vout与Vin传输特性。Ge pFET的离子对Ioff曲线说明了应变Si器件的改进特性。

使用垂直堆叠在Si层顶部的Ge层进行异构集成为CMOS逻辑实现提供了独特的机会,有助于扩展摩尔定律。

GaN主体上的Si施主晶片

上一节介绍了一种在Ge pFET中实现改善的空穴迁移率的方法。出现高级工艺开发问题的另一个领域是需要与常规CMOS逻辑集成的高效RF级设备。对5G(及更高版本)应用的需求要求毫米波功率放大器具有最佳的器件截止频率(Ft)和最大振荡频率(Fmax)响应,具有低噪声放大器相应的低噪声特性以及具有快速开关速度的RF开关。增强型GaN器件出色的Ioff和低Ron吸引了高效集成稳压器设计。

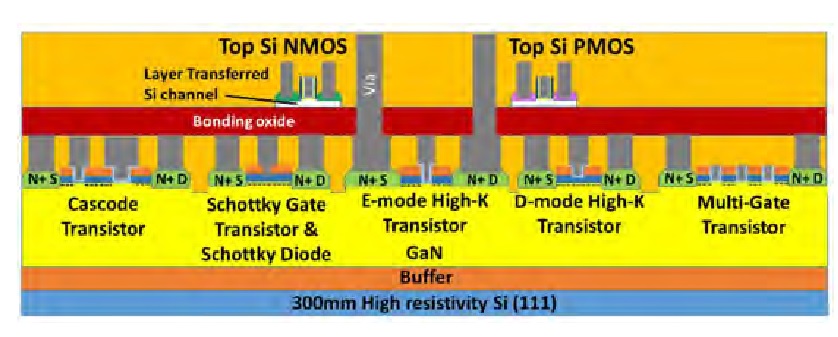

Gary强调了英特尔研究团队为开发GaN器件与常规Si CMOS电路的单片异构集成所做的工作。[2]

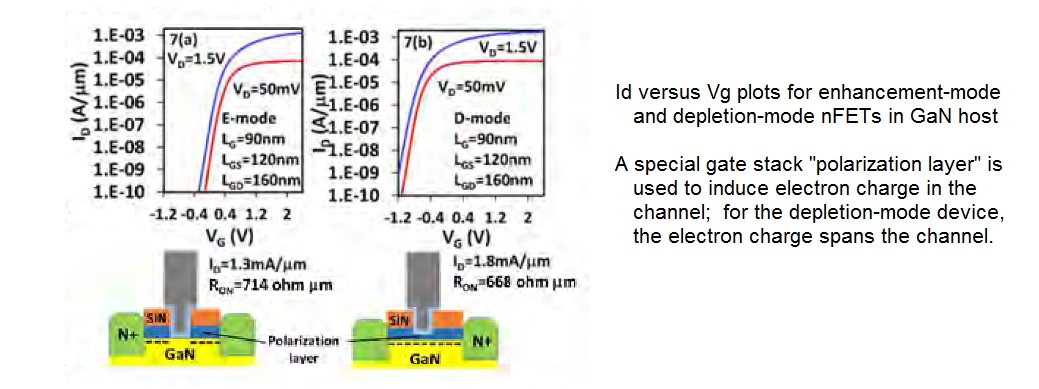

下图说明了在主机晶片(Si衬底)上的外延层中制造的各种GaN组件的制造-例如,增强型和耗尽型nFET,肖特基栅极FET和肖特基二极管(无高电平)。 -k栅极氧化物电介质)。还显示了最终结构的横截面。

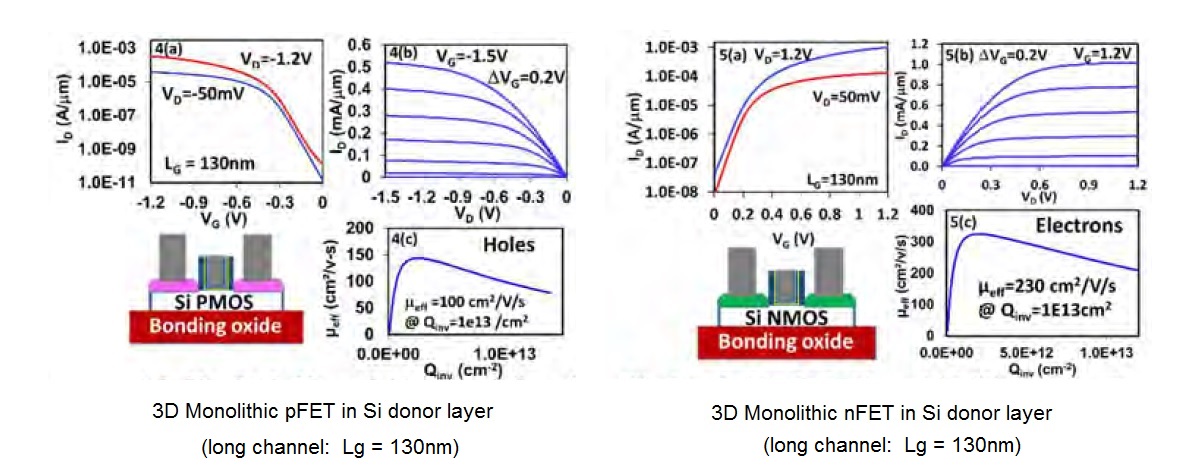

在这种情况下,施主晶片是Si,用于制造nFET和pFET器件,就像用于模拟功能,数字信号处理和逻辑/存储器一样。(P沟道GaN器件的制造极具挑战性。)

以前的Si nFET和Ge pFET单片集成的电路级CMOS集成需要一致的(且具有攻击性)设计规则,而(RF)GaN器件和(CMOS)Si器件的独特应用使这两种技术脱钩。与Si FinFET相比,GaN器件的尺寸可能与FET相差很大(例如,对于Ron非常低,W> 10um),或者具有更长的沟道长度以支持高压应用。

与在键合施主Ge pFET层之前制造的主体Si nFET一样,GaN器件也可以承受后续施主Si层转移和nFET / pFET器件制造的热预算。

下面显示了(长沟道)GaN增强模式和耗尽型nFET器件的典型Ids对Vg曲线,以及在施主层中制造的Si nFET和Si pFET器件的特性。

概括

FinFET器件在摩尔定律方面的下一个发展将是GAA拓扑。3D单片集成确实可以促进继续摩尔定律的机会,将用于SOI晶片制造的键合层转移技术扩展到更广泛的半导体材料,例如Ge和GaN。这将有助于减轻与引入“超越CMOS”材料工艺相关的风险。

对于从高性能计算到高频RF信号处理的各种应用,跟踪各种类型的设备的垂直堆叠的进展和创新将非常有趣。

结语

一位学术界人士在ASMC上通过的评论引起了我的注意。他说:“我发现学生对追求微电子学作为研究领域的兴趣正在减弱。他们听到“摩尔定律已死”,并得出结论认为这一领域已经停滞了。”

坦率地说,我想不起来比现在有更多的机会在设备研究,处理技术和电路/系统应用程序开发方面取得重大进展。如果您是阅读本文的学生,请意识到扩展摩尔定律有许多激动人心的地方。

源文地址:https://semiwiki.com/semiconductor-manufacturers/intel/299262-extending-moores-law-with-3d-heterogeneous-materials-integration/

版权声明: 本站内容除原创文章之外,转载内容只为传递更多信息,并不代表本网站赞同其观点。转载的所有的文章、图片、音/视频文件等资料的版权归版权所有权人所有。本站采用的非本站原创文章及图片等内容无法一一联系确认版权者。如涉及作品内容、版权和其它问题,请及时通过电子邮件或电话通知我们,以便迅速采取适当措施,避免给双方造成不必要的经济损失。联系电话:0756-8632035;邮箱:zhcce@chnchip.com.cn。

珠海市中芯集成电路有限公司是一家专业从事集成电路后序加工的高科技电子公司,可以为客户提供晶圆测试(wafer testing)、晶圆切割Dicing Saw(半切及贴膜全切) 、晶圆研磨减薄(wafer back grinding)、成品测试及tcp/cof/cob封装等全方位的服务。公司是中国半导体行业协会会员,珠海市软件行业协会副会长单位,获授国家高新技术企业,广东省“守合同重信用”企业,通过ISO 9001:2008和ISO 9001:2015体系认证。中芯的行为准则是“以客户为中心,以质量求生存,以服务求发展!”,希望通过我们的专业程度和不懈的努力,为客户提供低成本、高品质的产品。